Samsung Foundry, che è la seconda fonderia indipendente più grande al mondo dopo TSMC, ha apportato alcune modifiche al nodo di processo a 3 nm secondo Anand Tech. I primi chip di Samsung Foundry ad essere prodotti utilizzando il processo a 3 nm, 3GAE (3 nm Gate-All-Around Early), verranno prodotti in serie un anno più tardi del solito. Rimosso anche dalla roadmap di Samsung che 3GAE può essere prodotto solo per uso interno.

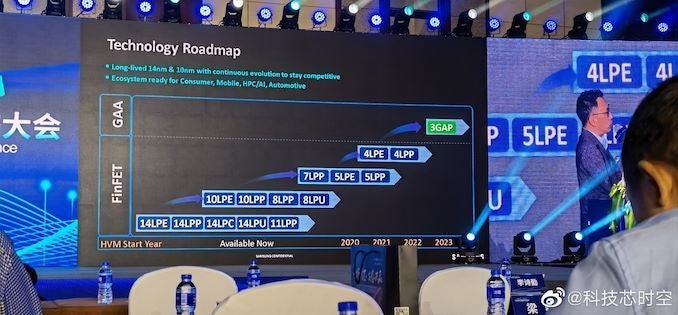

“Per il processo 3GAE, abbiamo discusso con i clienti e prevediamo di produrre in serie 3GAE nel 2022”, ha affermato un rappresentante di Samsung. Il successore di 3GAE, il nodo 3GAP (3nm Gate-All-Around Plus) è ancora sulla tabella di marcia poiché la produzione di volumi dovrebbe iniziare nel 2023. La tabella di marcia di cui sopra è stata rivelata al Foundry Forum 2021 in Cina. Samsung Foundry ha fornito la propria roadmap tecnica aggiornata che è stata poi ripubblicata su Baidu e Weibo.

Per quanto riguarda i chip che utilizzano l’architettura a transistor FinFET legacy, Samsung ha aggiunto 5LPP e 4LPP alla sua tabella di marcia con un lotto di produzione su larga scala rispettivamente per il 2021 e il 2022. quando Samsung ha presentato i suoi nodi 3GAE e 3GAP a maggio 2019 e ha annunciato che fornirà un aumento del 35% delle prestazioni e una riduzione del 50% del consumo energetico rispetto al 7LPP che è attualmente il nodo di processo della generazione precedente.

La roadmap di Samsung Foundry non mostra la produzione di massa del 2022 del nodo di processo 3GAE, probabilmente un’indicazione che verrà utilizzato per i componenti interni

Allo stesso tempo, nel 2019, l’inizio della produzione con 3GAA (Gate All-Around Transistor Architecture) è stato annunciato alla fine del 2021. Con la nuova data di lancio del 2022 per il processo 3nm Gate-All-Around Early, si può concludere che è un leggero ritardo da parte di Samsung o un errore di calcolo. Ad ogni modo, non è un grosso problema poiché i primi nodi di Sammy non sono utilizzati in larga misura dai produttori.

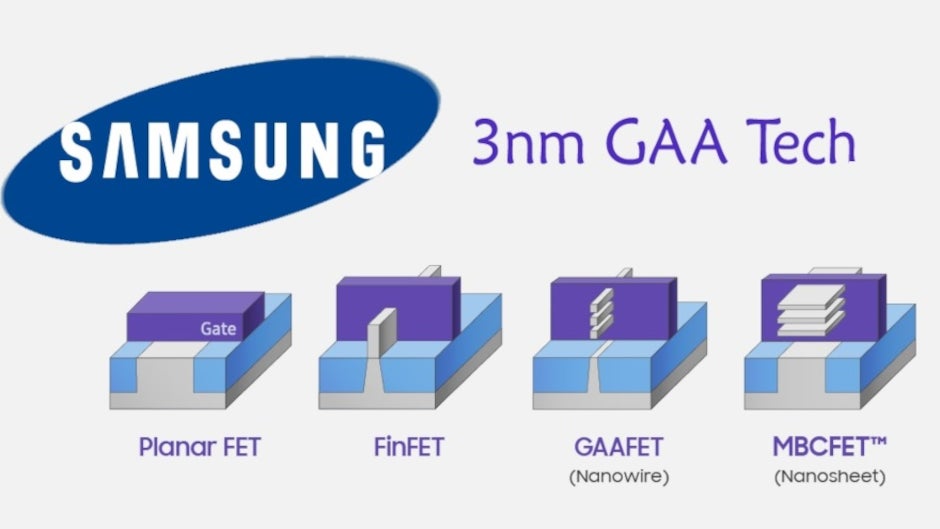

Solo pochi giorni fa, Samsung Foundry ha registrato un chip da 3 nm che utilizza l’architettura a transistor Gate-All-Around (GAA). L’espulsione di un chip è l’azione finale del suo ciclo di progettazione che porta a uno di questi due risultati: la progettazione del chip funziona o meno. In quest’ultimo caso, può essere necessaria una revisione minore o una revisione del progetto.